|

||

|

Senior Member

加入日期: Feb 2002 您的住址: 宜蘭

文章: 1,341

|

引用:

你有看過連結內容? 內容所提的 on-die magnetics 指的是在 VRM 的 on-die magnetic layer. 主要在討論 CMOS 整合磁性物質的製程方式的突破.. Haswell (包含 cpu 設計的 power plane separation ) 整合 On-chip(package) VRM, 優點就是 fine grain power control. 每個 CPU 核心 / GPU 模組 / MCH 都可以有同時不同的DVFS組態. 在講求電源效率的ARM SoC 上Qualcomm / Samsung 等都已經實作 power domain / frequency domain separation + power gating.

__________________

AMD Athlon 64 3000+ Asus A8N-E nfoce 4 empowered Simems DDR 400 512MB *2 Benq 1640 --------------------------------- |

||||||||

|

|

|

Elite Member

加入日期: May 2002 您的住址: 板橋

文章: 5,112

|

引用:

Multiple power domain/power gating是可以提高電源管理的效率,不過要把數十W級的VRM兜進去(不論是on die或MCM)在短時間內都不是開玩笑的   .... ....

__________________

士大夫之無恥,是謂國恥   .... ....

|

|||

|

|

|

Senior Member

加入日期: Feb 2002 您的住址: 宜蘭

文章: 1,341

|

引用:

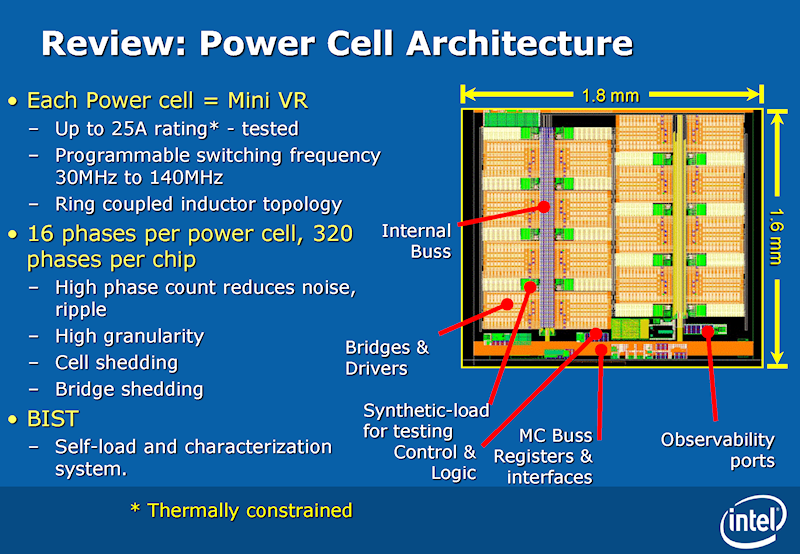

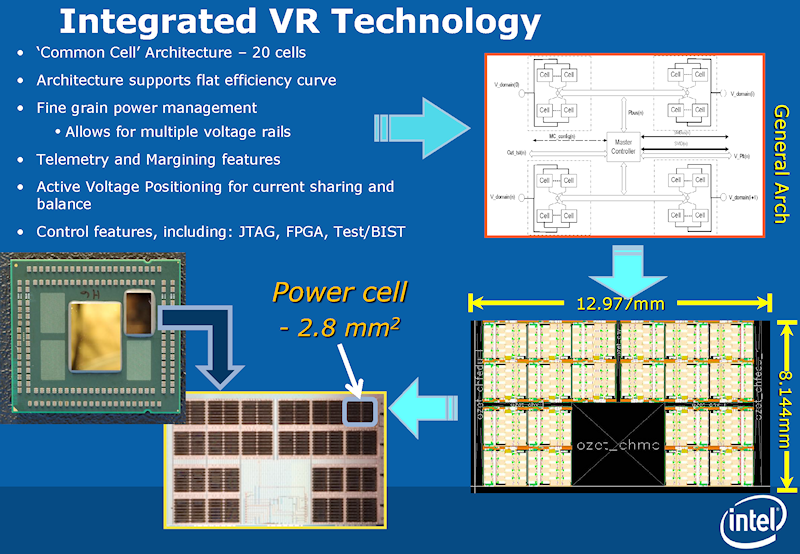

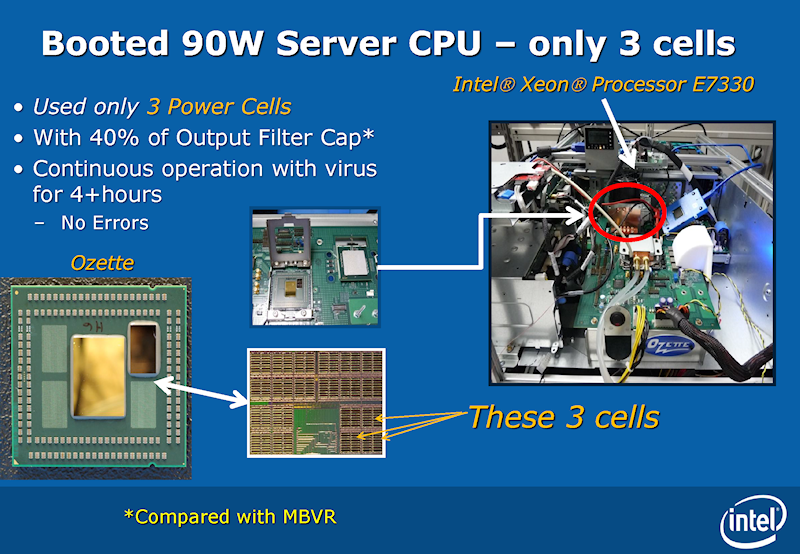

Power Cell 組成, 16向, 最高單 cell 可以支援到25A, 可編程頻率30~140MHz  Integrated VR Chip, 20 個 Power cell  E7330 with Integrated VR. 90W. 僅用3個 power cell.  幾年前就有實際樣本測試過了...最高支援到400A, 測試至220A( 限制於散熱 ) http://www.psma.com/sites/default/f...e-regulator.pdf Conclusions • 400A capable – tested to 220A for less than 1⁄2 of chip - Board thermally limited. • Booted and ran server processor (90W design) with 2 cells – ran with 3 cells under LinpackTM for 4+ hours. • Ripple below noise threshold • Efficiency in low 80’s with minor changes -Additionalchangespossiblewillboostup. • Density is ~8A/mm2 thermally constrained

__________________

AMD Athlon 64 3000+ Asus A8N-E nfoce 4 empowered Simems DDR 400 512MB *2 Benq 1640 --------------------------------- |

|

|

|

|

Master Member

加入日期: Sep 2003

文章: 1,810

|

> 你有看過連結內容?

當然有 > 主要在討論 CMOS 整合磁性物質的製程方式的突破.. 這只是一部分,而且講的是如何用磁性物質提高電感值(可達9倍之多) 有助於縮小電感面積 我上一篇講的是文中提到是與消費者更加相關的那一部分 雖然這只有幾行字 幾張照片,但對消費者來說遠遠比這篇大部分的文都要來的有價值 如果你覺得我沒看過的話,我想你忽略的這些資訊 > > 結果電感不是on-die,是on-package 我上面這一行用錯詞了 及少註明東西 電感要換成CMOS voltage regulator,雖然CMOS voltage regulator 大部分是電感 另外 CMOS voltage regulator 是on-die(on 他自己的die),不是on在CPU那個Die 所以後藤弘茂稱這個方式叫on-package 此文章於 2013-01-04 04:10 PM 被 orakim 編輯. |

|

|

|

Senior Member

加入日期: Jan 2004 您的住址: 高雄市

文章: 1,244

|

有一個疑問

為什麼英特爾不推出高電壓低電流的產品(同瓦數) 這樣在AC轉換DC時效率不就能夠提高很多嗎!? 在以前個人PC當道的時代,這樣做不是能減低很多損耗嗎!? |

|

|

|

Senior Member

加入日期: Dec 2002

文章: 1,370

|

引用:

因為 CPU 功耗與電壓的平方成正比.

__________________

要討論也要找能溝通的, 跟狂吠的狗溝通只是浪費時間. 每日一句 : 很多不等於多數,也不等於少數 |

|

|

|

|

Junior Member

加入日期: Mar 2012

文章: 733

|

引用:

應該不是這樣吧!!!! 理想的CMOS 功耗損失來自於電壓狀態切換損失......功耗應正比於頻率.... 當然不可能有理想CPU......得看其製程漏電率......通常電壓越高漏電劣化程度越高.. 另外電壓越高....代表狀態切換swing的時間就越長...動作頻率會較低........ 所以要廠商直接做12V vcore CPU不是不可能....但速度應該會慢很多吧......而且狀態切換漏電損失應該頗為可觀吧... |

|

|

|

|

Elite Member

加入日期: May 2002 您的住址: 板橋

文章: 5,112

|

引用:

這要分兩部份解釋,高工作電壓就要高耐壓,通常代表絕緣層要變厚,整體的體積就會變大(電子要走的路徑變長),所以不利於高速化(以早期的製程為例,CMOS的耐壓/工作電壓最高,速度最慢,TTL居中,速度也居中,ECL工作電壓最低,速度也最快,不過ECL最快不單是工作電壓低一項因素而已  ),另一方面高工作電壓通常代表邏輯位準也會跟著升高,光看邏輯位準轉換時耗在寄生電容上的能量(Q=CV)就跑不掉了,so ),另一方面高工作電壓通常代表邏輯位準也會跟著升高,光看邏輯位準轉換時耗在寄生電容上的能量(Q=CV)就跑不掉了,so  .... ....此文章於 2013-01-04 06:47 PM 被 cmwang 編輯. |

|

|

|

|

New Member

加入日期: Jan 2013

文章: 1

|

為什麼不要低電流?

數位電路講求低電壓高電流速度才會快 POWER整合在CHIP上應該也還好,看那面積那麼大 CHIP也沒想像中的不耐流,PAD用多一點、走線粗一點就是了 |

|

|

|

Master Member

加入日期: Jul 2001 您的住址: 天堂

文章: 1,688

|

Haswell用的是VR 12.5

VR 12.5還是獨立的 只是整合控制器而已 但已經讓主機板設計變簡單很多 真正整合要到下一代Broadwell看有沒有機會 我手上還有12.5的spec...

__________________

初學者的無知在於未學,學者的無知在於學後... 你曾經愛過的人使你失望之後, 他看起來就似乎有了許多缺點。 Schultz 人格理論 |

|

|