|

||

|

*停權中*

加入日期: Sep 2001

文章: 616

|

引用:

感謝回覆。 看了參考資料,我可否簡略歸納:hi-k 是為了降低漏電流(省電)、low-k 是為了降低 delay(高速)? |

||||||||

|

|

|

Power Member

加入日期: Jan 2004

文章: 573

|

引用:

TDP什麼時候變成功率消耗值了阿 我想太多人搞錯意思了吧  TDP:熱消耗設計規格(Thermal Design Power) TDP是指CPU電流熱效應以及其他形式產生的熱能 TDP功耗可以大致反映出CPU的發熱情況 但是TDP並不等於CPU的功率消耗 |

|||

|

|

|

Power Member

加入日期: Jan 2004

文章: 573

|

引用:

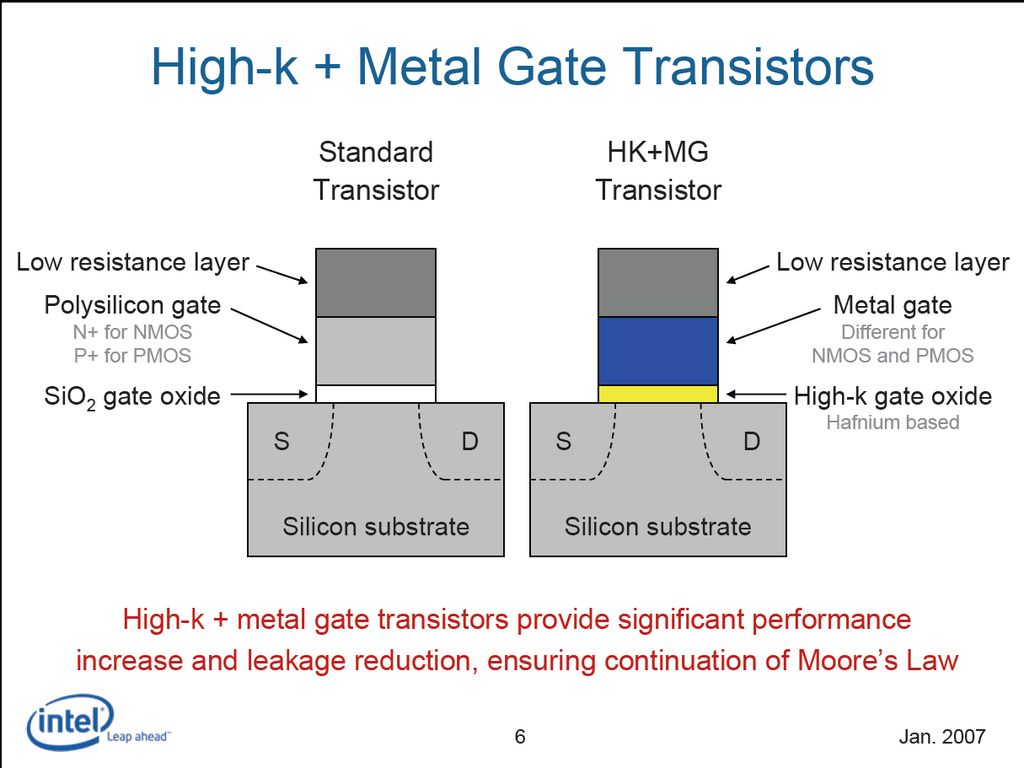

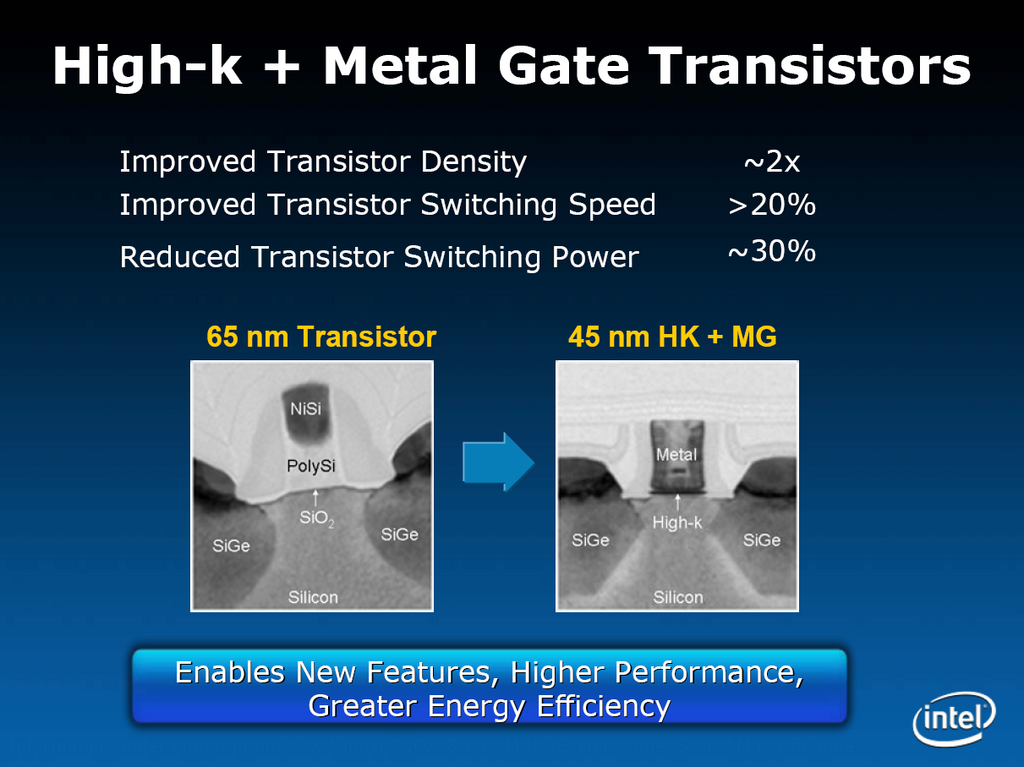

簡單說起來是這樣子沒錯啦 所以其應用的地方不同 製程不斷縮小,連帶的電晶體閘極的絕緣層也越來越薄,反而使得漏電流增加,為了克服漏電流問題所以才會在閘極絕緣層使用high-K 材料 |

|

|

|

|

*停權中*

加入日期: Sep 2001

文章: 616

|

引用:

感謝回覆。  |

|

|

|

|

*停權中*

加入日期: Nov 2006

文章: 3,946

|

引用:

那是因為以前TDP跟實際耗電量很接近  |

|

|

|

|

*停權中*

加入日期: Jun 2004 您的住址: 中華民國

文章: 764

|

同時脈效能輸

拉時脈潛力輸 耗電量也輸 |

|

|

|

*停權中*

加入日期: Oct 2004 您的住址: 台北

文章: 3,188

|

只有CMOS嗎

high k跟low k狀況不同,low k是看有沒有需求,C不見得越小越好,可是high k有他的需要,因為sio2那層已經達到極限了,10A左右已經快低於一層分子的厚度了,所以再加上一層high k避免電子直接穿過gate上面,是有迫切的需求性,自從.13的14a之後這問題就很重要了。gate電流會出來,國內不知道有沒有這樣的製程,國外有bism4這個東東,low k不見得能讓速度提高,還有另外的問題存在。不過high k才能讓整個功能性正常,才不會通過gate到底是什麼電流都搞不清楚。 |

|

|

|

*停權中*

加入日期: Sep 2006 您的住址: 北台灣

文章: 311

|

引用:

大哥, 那些只靠張嘴巴吃飯的媒體人半吊子言論, 您也信的太多了吧 .....  鎖國  台灣根本已經太過開放, 今天才能成為中國大陸第二位的外資投資國. 台灣根本已經太過開放, 今天才能成為中國大陸第二位的外資投資國.聯電降低成本佈局大陸, 那是他們家的事, 大家 care 的重點是作這些佈局的同時, 是否有考慮到台灣眾多投資股東的利益 & 員工的工作權益 ? 是否違反企業治理的原則, 把員工辛苦研發的專利雙手奉給和艦 ? 當然, 也可以拿為了降低成本當作理由, 為達目的不擇手段, 但是, 這是對的嗎 ? 曹董還在那裡推跟大陸統一, 哇嘞 .......  |

|

|

|

|

*停權中*

加入日期: Sep 2001

文章: 616

|

引用:

感謝回覆。 雖然我曾跟您吵過一次,但我對您的學識還是深表敬佩,也感謝您不吝指教  。 。 |

|

|

|

|

*停權中*

加入日期: Oct 2004 您的住址: 台北

文章: 3,188

|

C不C的cmos

|

|

|