|

||

|

Power Member

加入日期: Nov 2004

文章: 693

|

引用:

高見 高見    FinFET不是intel發明的 至於TSV intel則挑戰失敗 停留在實驗性質的階段 3D Nand Flash業界第一個實現48層堆疊是東芝/SanDisk 但是東芝即使有3D Nand 另外也在開發TSV堆疊 TSV貫通接點的優點 可不是「紙箱攤平」的堆疊能達到的 紙箱攤平是有點抽象化 不過這就是所謂3D結構的現狀 東芝、世界初のTSVによる1チップ256GBのNANDフラッシュ 東芝、NANDフラッシュとSSDの開発戦略をFMSで公表 |

||||||||

|

|

|

*停權中*

加入日期: Aug 2015

文章: 53

|

引用:

那請問3D封裝與2.5D封裝的主要差別是? |

|||

|

|

|

Senior Member

加入日期: Feb 2002 您的住址: 宜蘭

文章: 1,341

|

引用:

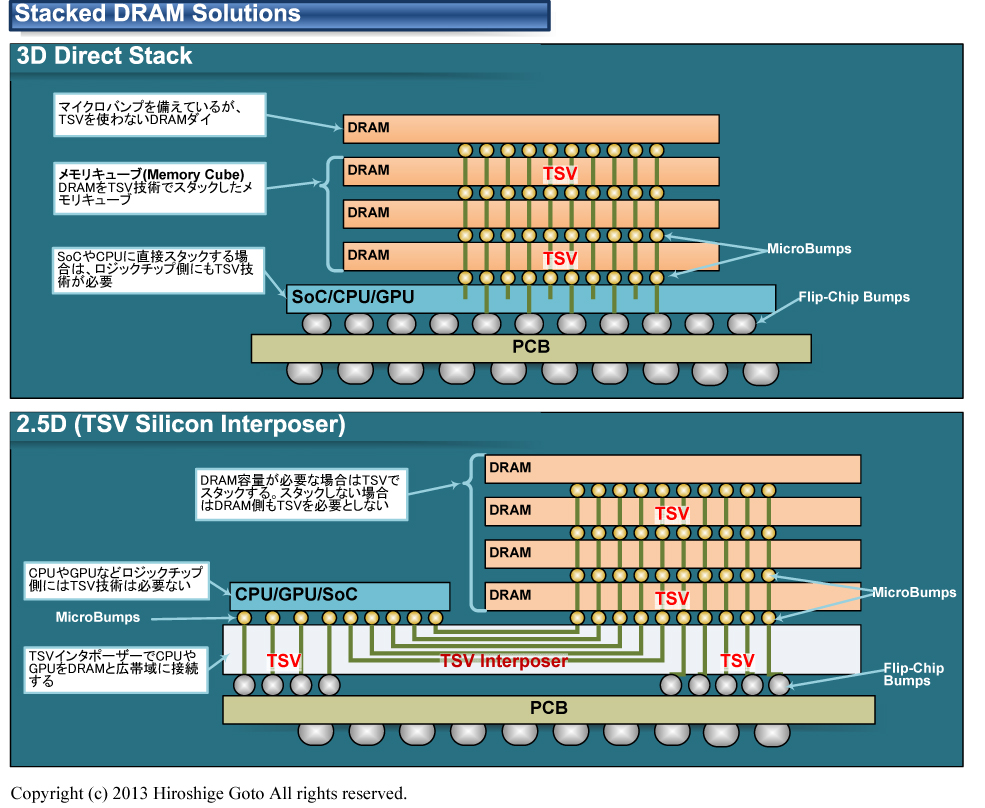

3D: TSV 直接堆疊 2.5D: TSV + Interposer 應該吧

__________________

AMD Athlon 64 3000+ Asus A8N-E nfoce 4 empowered Simems DDR 400 512MB *2 Benq 1640 --------------------------------- |

|

|

|

|

*停權中*

加入日期: Aug 2015

文章: 53

|

引用:

我也是這麼認為,可是樓上說是分開的 |

|

|

|

|

Power Member

加入日期: Nov 2004

文章: 693

|

引用:

那一定是你可能有誤會    pcwatch圖解  |

|

|

|

|

*停權中*

加入日期: Aug 2015

文章: 53

|

引用:

別這樣,誤會的是樓上又不是我  |

|

|

|

|

*停權中*

加入日期: Jun 2015 您的住址: 金一十大女支三

文章: 1,282

|

引用:

你只能google當然看的層面就很有限 這種東西就是要回到IEEE paper上去看 早在2008左右 這些3D IC的概念就有各種不同的做法被提出 製程的東西 日本人從來都排不上邊 台灣都比他們強 而且我們的半導體製程怎麼算也是世界前五以內 這麼關心這方面 是靠這個吃飯嗎? 不管哪一家的3D IC 用甚麼概念實現 最後還是回歸到密度 良率 成本 這幾個老議題 所以並不是技術先進就會現階段採用 TSMC最強大 或者說台灣最強大 就是代工良率佳而且價格不錯... 意思就是我們很會cost down  |

|

|

|

|

Power Member

加入日期: Nov 2004

文章: 693

|

引用:

你真的有看過相關論文? 真是不可思議    |

|

|

|

|

Major Member

加入日期: Jan 2007

文章: 248

|

引用:

他說的確實是如此 3D IC在很早就有paper講,可上IEEE查詢 另外,除了所謂的TSV 還有些單晶片的3D IC概念 是利用Inter Layer Dielectric分隔上下兩層,再以internal contact 連接 這就已經算是3D IC了。 double gate MOSFET 也是3D IC,追朔可以更早 現在的問題是你說的3D跟我說的3D是不是同一件事 就像MOSFET從微觀角度也是3D,它也有XYZ三軸座標 但從巨觀的角度看,MOSFET都是座落在XY平面上 雖然有Z(高度),巨觀來看可以說是2D |

|

|

|

|

Advance Member

加入日期: Jan 2003

文章: 357

|

引用:

3D 封裝是 die 上疊 die(目前的方案). 2.5D 是異質 die 封裝成一個 IC, 不使用 wafer level TSV. 還有, 3D 封裝是晶圓廠的強項, 穿孔在電路 die 上. 而 2.5D 是只用 Si 基材的 TSV, 相對門檻低很多很多, 所以一般封測廠能做. 此文章於 2015-09-21 01:46 PM 被 wwchen 編輯. |

|

|

|