|

||

|

Power Member

加入日期: Nov 2004

文章: 693

|

HBM第一世代29nm製程

第二世代個人猜測是20nm 不過 最難的是傳輸介面的基頻提升一倍 頻寬也提升一倍 (記憶體內部的頻寬遠大於外部頻寬) HBM2到現在還沒有展出晶圓 ...還須要時間 |

|||||||

|

|

|

Advance Member

加入日期: Jan 2003

文章: 357

|

引用:

忘了說! 你要了解這方面訊息, 請看正統的. 例如這篇: 3D IC pakage https://zh.wikipedia.org/wiki/%E4%B...%99%B6%E7%89%87 所謂的 HBM 不過是上述的其中一種. 關鍵技術是 TSV. 源頭構想不外乎來自 製造成本. 增加記憶體的頻寬是看系統設計, 不一定是要靠堆疊. 此文章於 2015-09-17 09:21 AM 被 wwchen 編輯. |

|||

|

|

|

Power Member

加入日期: Nov 2004

文章: 693

|

裸晶沒那麼快釋出

飼食都不夠還想曬乾 引用:

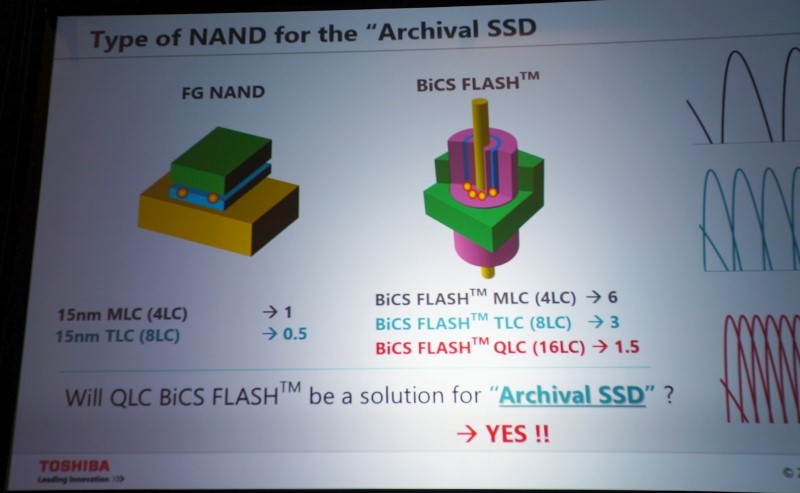

不是在討論TSV的HBM嗎 ? 怎麼變成FinFET    就算討論FinFET 台積電目前也沒有優勢 目前3D晶圓也就三種 1.FinFET 2.3D Nand Flash 3.TSV 4.可能是東芝在研發的QLC Nand Flash  就性質而言 1&4接近 屬於積體電路最小的元件 電晶體架構3D化 2&3都是屬於堆疊型3D (另外 TSV可貫通接點) |

|

|

|

|

Power Member

加入日期: Nov 2004

文章: 693

|

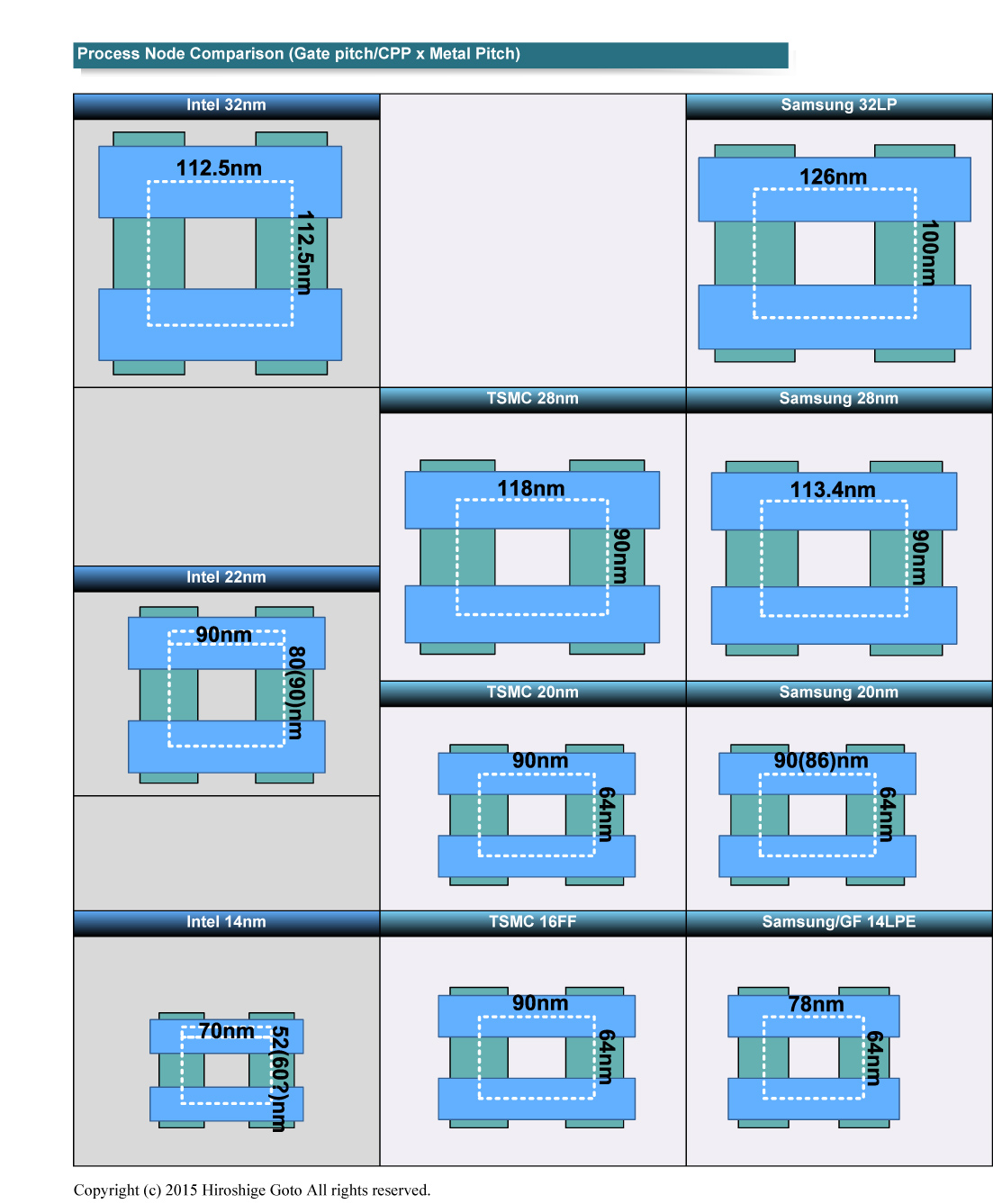

FinFET系 台積電是較差的 至少目前是如此 |

|

|

|

Major Member

加入日期: Dec 2006

文章: 194

|

引用:

雖是這樣 , 不過三星後段製程有問題,導致APPLE的A9晶片,他的14nm最後產出的晶片竟然比tsmc的16nm晶片還要大,更重要的是良率跟tsmc差了一大截 這也是最後TSMC的單會後來從3:7最後拉到5:5,跟三星同樣 甚至謠傳TSMC A10全拿 |

|

|

|

|

*停權中*

加入日期: Aug 2015

文章: 53

|

引用:

請問3D封裝要如何解決堆疊晶片的散熱問題? |

|

|

|

|

Power Member

加入日期: Nov 2004

文章: 693

|

引用:

無解 能應用高頻寬記憶體的邏輯晶片一定是暴熱的 目前正3D堆疊應用只有紙上規格的Wide I/O 之前有媒體拿來和HBM比較 很懷疑寫稿的人到底有沒有了解Wide I/O是啥? Wide I/O是給低功耗/超低功耗使用的 本身的功耗較低 性能(頻寬)也低 Wide I/O2 一顆八通道 頻寬只有51.2GB/s 而且只堆疊「2層」 正3D堆疊應用 最底層要控制到臨界溫度以下是很嚴苛的 2.5D亦然 HBM 8Hi Stack 的使用環境也是有限制的 此文章於 2015-09-17 11:50 AM 被 st202 編輯. |

|

|

|

|

*停權中*

加入日期: Jun 2015 您的住址: 金一十大女支三

文章: 1,282

|

NV的HBM預計會在2017出現 Pascal有非常大可能沿用GDDR5

NV只是慢一點 又不是拿不到 這不是甚麼記者寫的 國外論壇一樣有雙方工程師出沒 工程師不能上網打屁喔? 這種東西有甚麼好造假 就一個既定事實 早就在生產 產線要改有那麼簡單嗎 HBM是HBM TSV是TSV 不要混為一談好嗎 TSMC拿到訂單是好事 這家是台灣少數良心還在公司 希望張忠謀活久一點 上次亂接班差點鬧出亂子 破壞容易建設難 引用:

你都知道這兩者不同 還要求用TSV稱呼HBM 真怪 TSV算一種製造技術 HBM是一種結構 這兩個能夠一名詞通稱? ------------- 對Through-Silicon Via, TSV製造出來相關技術有興趣 就直接用關鍵字搜尋paper 會有更多專業內容 技術的東西google沒用 這不是給一般人看的 此文章於 2015-09-17 12:06 PM 被 lzarconlony1 編輯. |

|

|

|

|

*停權中*

加入日期: Aug 2015

文章: 53

|

引用:

謝謝解惑  也就是說GPU相關應用等於直接宣告出局對嗎?那正3D到底能應用在甚麼地方呢? 也就是說GPU相關應用等於直接宣告出局對嗎?那正3D到底能應用在甚麼地方呢? |

|

|

|

|

Advance Member

加入日期: Jan 2003

文章: 357

|

引用:

我的意思是: 所謂的 HBM 是透過 3D 封裝技術, 並不是啥新鮮 東西. 而完成的必要技術是 TSV. 老實說: 我會用 3D pakage 統稱之. 所以, 也沒有什麼 NV 不能做滴! 還有 Hi bandwith memory 不一定要靠堆疊, 用設計即可. 一切是以成本考量. 目前用 2.5D 封裝是比較合成本. 而且, 記憶體也即將由 20nm 進化至 10nm(2020 年前), 單位 die size 可塞入更多電晶體. AMD 的圖示顯示為 3D 封裝, 真有這必要嗎? 別忘了, 這幾年 16nm, 10nm, 7nm 的進化相當快速. 回應樓上說散熱問題: 就是工藝進化能解決, 並非無解, 是比較難解而已. 我的擔憂反而是 TSV 的製造技術是否能夠耐得住大量生產!? 穩定度有待考驗. 架構要設計有許多大廠都會, 但製造技術才是 關鍵. 可以設計成圓球形的建築沒錯, 但工程公司的技藝如何, 才重要. |

|

|

|