引用:

|

作者hareluya6510

我想應該是我描述的不夠清楚

3D NAND個發展概念就是為了增加容量

當製程沒辦法再微縮, 搭上Multi Level Cell 或是 Triple Level Cell都無法再增加容量時

就會朝垂直方向的堆疊(就是第4點), 這才是3D NAND, 前面3點只是講古

至於MOS是不是只有一層

我想我應該用另一種說法

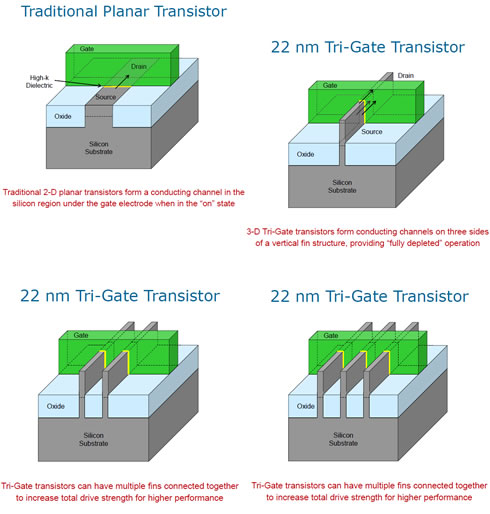

當你把現在2D MOS的gate dielectric 轉90度後跟3D MOS比

你就會發現, 現在的2D MOS確實只有一層

|

要放就放給你看

請問要怎麼轉planar transistor才不是3d?

2d mos只是相對於現在3d trigate而言,實際上他怎麼會不是3d?

intel跟ibm的copper wire interconnection又算不算你所謂的3d結構?

會搞成這樣的原因就跟前面的"無敵金鐘罩"犯了一樣的錯

他拿intel的"3d transistor"來說明3d ic,這兩者根本是完全不同的東西

你只要去搜尋一下甚麼是2.5D ic,甚麼是3d ic就知為啥我會說那不是3d ic

只是立體結構,而且已經做很久了....